# Semiconductor

|    |   | _          | _   |    |

|----|---|------------|-----|----|

| 20 | - | <b>Ima</b> | air | na |

|    |   | IIIIG      | MII | ιч |

| Name: |

|-------|

|-------|

| In-C   | lacc | Pro | Ы   | ωm | • |

|--------|------|-----|-----|----|---|

| 11 I-C | ıass | riv | IJΙ | em | з |

#### This is it! Last in-class HW session!

Note – this 1<sup>st</sup> problem is a new problem I just developed for CCD imaging devices. It may require some tweaks during class. If you crash out at any point, let me know quickly and I will revise it accordingly!

- (1) Lets start out with a CCD imaging device, which is a good refresher for MOSFETs since the charge collecting well (a.k.a. the 'bucket') for a CCD pixel is just a MOS capactor. We will go back into topics from way earlier in the course in order to do this (a nice wrap-up problem!).

- (a) Draw a simple band-diagram for an ideal MOS capacitor in a CCD imager with positive voltage applied to the gate (such that it creates a 'bucket' to capture photo generated electrons). Assume the substrate is p-type. Note, your 'metal gate' is likely something like ITO (discussed last lecture) which is a wide-bandgap and therefore transparent semiconductor. For simplicity, assume an ideal MOS capacitor. *Hint: see slide 7 in the lecture*.

- (b) Next draw another diagram that shows how you will use positive voltage across multiple gates to moves charge to the edge of the array where it can be recorded by electronics. *Hint: see slide 9 in the lecture.*

- (c) Next let's deal with how much light is hitting the semiconductor. Assume that on average we irradiate the device with  $2x10^{12}$  photons/cm<sup>2</sup> every second, and that nearly all of that visible-spectrum light is absorbed in the first 2  $\mu$ m of semiconductor beneath the oxide (*I got this from slide 14 lecture 15*). That is about 0.7  $\mu$ W/cm<sup>2</sup> (not needed for your calculation, is just so you have some frame of reference, see slide 11 of week 15 for how to calculate). First, calculate the optically generated excess carrier concentration assuming that carrier lifetimes due to recombination are  $\tau_n \sim \tau_p = 10$   $\mu$ s. Hint, use this equation from slide 12 week 15, which tells you how recombination and optical generation balance out. You will need to convert the above info to  $g_{op}$  (1/cc-s) which is actually quite easy if you think about it. Make sure you keep units consistent!

$$\delta_n = \delta_p = g_{op} \tau_n = g_{op} \tau_p$$

- (d) Assume the substrate is doped to 10<sup>15</sup>/cc with Boron. Question: how does that compare to your result from (c) in two ways: <u>first</u>, how big of a change (in terms of general orders of magnitude) is the concentration for electrons, and <u>second</u> is the change in holes below the doped level? (which is important, because you need dopings for semiconductor devices to work, and if the optical or thermally generated carriers are even more than the doped levels, then your device is likely in trouble).

- (e) So hopefully in (d) you showed that you are setup for success: a large change in the minority carrier concentration due to light, and you are not overwhelming your doped majority carriers. Next, calculate the maximum depletion width

#### SECS 2077 - Semiconductor Devices Homework

that can be achieved <u>and</u> calculate <u>the diffusion length</u> for electrons in this material. *Hint: use this equation found on slide* 23 in the lecture for week 12.

$$W_m = 2\sqrt{\frac{\varepsilon_s kT \ln(N_a/n_i)}{q^2 N_a}}$$

Remember, diffusion length is just the square root of diffusion coefficient times lifetime. Assume for this doping level electron mobility is ~1000 cm/s/(V/cm). And you can use this equation from lecture 2.

$$D_n = \mu_n kT / q$$

As you complete this calculation, you will notice that W+Ln is much longer than the depth of photon absorption stated in part (a), and therefore when you go onto the next part you should replace (Ln+Wm) instead with just the 2 µm which was stated in part (a). This may not always be the case (e.g. higher doping levels which shorten Ln and Wm and longer wavelengths of light which have weaker absorption in Si).

(f) Whew, almost there. Next.... assume the pixel area is 100 μm x100 μm (these are the horizontal dimensions of the 'bucket'). Calculate the optical generated current if light were continually shining on this 'bucket' beneath the MOS capacitor. Hint: use this equation from slide 9 in the lecture and do the substitution mentioned above! Remember, careful with units!

$$I_{op} = qg_{op}A(L_n + W_{\text{max}})$$

(g) Finally... figure out the amount of charge you will collect in this bucket per frame if we have a frame rate of 60 Hz. *Equation below is also from slide* 9. This is how much charge some sort of amplifier at the edge of the CCD will receive in order to read the pixel. *With 'some electronics', if you wanted, you could design the rest of what is needed to make the CCD work.*

$$Q_{op} = I_{op} \times t_f(s)$$

The answer might seem small, but if your CCD had 1000x1000 pixels (1 million pixels), then at MINIMUM it would need to read out this charge per pixel in 1 µs or faster. That leads to a decently large current (charge/time). In practice, the read out will have to be much faster than that, because the CCD spends most of its time just sitting there collecting light in its 'buckets', then doing a super-fast movement of all the buckets to the read out electronics, then repeating that process.

- (2) Now let's switch gears to CMOS imaging arrays. CMOS imaging arrays are faster because they have at least one CMOS transistor at each pixel and therefore can be addressed using row-column addressing (less of a serial scanning process). This also means you can get to higher pixel densities. They also require less power. And, they can be made using CMOS fabrication lines: lots of existing manufacturing infrastructure and tools, which reduces their cost. This lower cost, is their biggest advantage commercially. Now....

- (a) As shown in the image at right, they use monochrome Si CMOS pixels that are covered with RGB color filters, but there are twice as many green filters as red or blue. Why? Hint, we covered this in today's lecture 20, or you can remember the LEDs lecture and Im/W (brightness) for colors as they are perceived by the human eye.

- (b) Here is a commercial CMOS chip.

MT9P031: 1/2.5-Inch 5Mp Digital Image Sensor Features

## 1/2.5-Inch 5Mp CMOS Digital Image Sensor

MT9P031 Data Sheet, Rev. G

For the latest data sheet, refer to Aptina's Web site: www.aptina.com

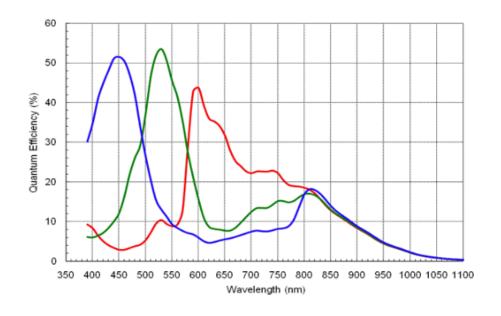

Notice the 1st plot below from the spec sheet for this chip, which is quantum efficiency vs. wavelength. Quantum efficiency for a photodiode or an imaging array = (# electrons collected / # photons in). The color filter effect on quantum efficiency is easy to see and obvious (if a color filter absorbs light outside of the desired wavelength range, that absorbed light is absorbed in the color filter material where it does NOT generates electrons.

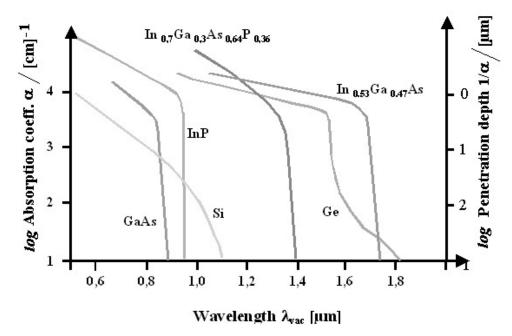

Question: notice how the quantum efficiency generally decreases as you get closer to the bandgap energy of Si (Eg= 1.12 eV= 1240 / 1107 nm). Why is this? Hint, see the second plot below which is from lecture 16 on photodiodes.

### (4) Some more old-timey review from lecture 3:)

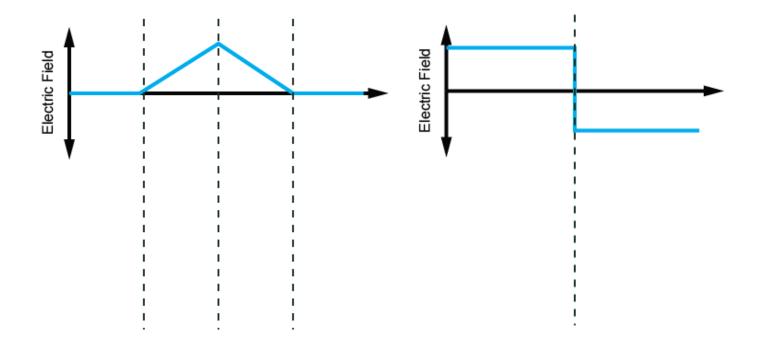

E-field causes band diagrams to have slope! Anytime you have E-field, you know it means the bands must bend! Redraw each of these E-field plots on the board, and below the E-field plots draw the corresponding band diagrams (don't worry about the Ef or dopings, just plot the conduction and valence bands).

To help solve this problem, use the electrons=water and holes=bubbles analogy and think how they each should move (left or right) in the E-field. Assume the E-field is measured in the direction from left to right. Remember, higher E-field should make the bands slope steeper! (postive E-field = positive bands slope / negative E-field = negative bands slope).

- (5) And... last bit of old-timey review from lecture 7 : )

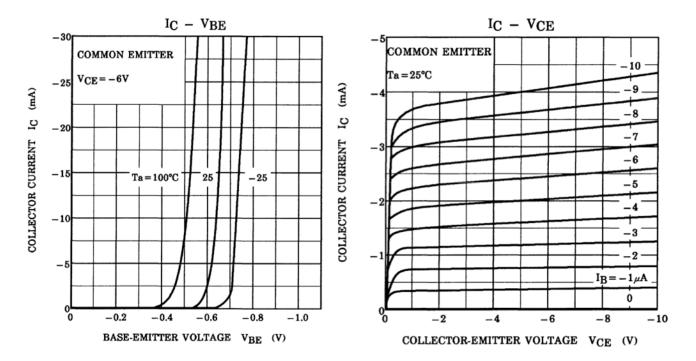

- (a) See the spec sheet I-V curves below. Why is  $I_C$  exponential vs.  $V_{BE}$ ? The answer is simple.

- (b) See the spec sheet I-V curves below. For Ic vs. Vce, what is the amplification factor (Beta)? To be sure, pick 2 or 3 base-currents and collector currents to calculate Beta.

- (c) See the spec sheet I-V curves below. As Vce is increased it takes a little bit (looks like  $\sim$ 0.5V) to get the BJT amplification going. Question: basically all the Vce voltage drop occurs where in the BJT? ... and why is the collector current fairly constant as  $V_{CE}$  is further increased?

- (d) Based on your answer to (f), that increasing Vce should increase the base-collector depletion region, right? An increasing depletion region should cut into the base and reduce Wb (the un-depleted width of the n-type base). So, if increasing Vce reduces Wb a bit, then why the slight positive slope for Ic vs. Vce?

(6) And... very last: https://www.youtube.com/watch?v=b9434BoGkNQ